# High Speed SAMPLE/HOLD AMPLIFIER

## FEATURES

- 350ns max ACQUISITION TIME

- ±0.01% THROUGHPUT NONLINEARITY

- 150ns max SAMPLE-TO-HOLD SETTLING TIME

- INPUT BUFFER (SHC803)

- 24-PIN HERMETICALLY-SEALED METAL PACKAGE

## DESCRIPTION

The SHC803 and SHC804 are high speed sample/hold amplifiers designed for use in fast 12-bit data acquisition systems and signal processing systems. The SHC803 contains a fast-settling unity-gain amplifier for buffering high impedance sources or for use with CMOS multiplexers.

The SHC804 acquires a 10V signal change in less than 350ns to  $\pm 1/2$ LSB at 12 bits. Throughput nonlinearity

error is guaranteed to be within  $\pm 1/2$ LSB for 12-bit systems. Stability over temperature is excellent, with only  $\pm$ 5ppm/°C of gain drift and  $\pm$ 4ppm of FSR/°C of charge offset drift over the –25 to +85°C temperature range.

The  $\pm 25$ ps maximum aperture uncertainty of SHC803 and SHC804 permits sampling (to  $\pm 0.01\%$  of Full Scale Range) of signals with rates of change of up to  $100V/\mu$ s. These sample/holds have been optimized for use with Burr-Brown's high speed 12-bit analog-todigital converter, model ADC803. Together these components are capable of accurately digitizing fast changing signals at sample rates as high as 500k samples per second.

The digital inputs (HOLD and  $\overline{\text{HOLD}}$ ) are TTLcompatible. Power supply requirements are ±15V and +5V and the specification temperature range is -25°C to +85°C. The SHC803 and SHC804 are packaged in a 24-pin dual-in-line hermetic metal package. SHC804 is pin-compatible with other sample/holds on the market with similar performance characteristics.

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

## **SPECIFICATIONS**

### ELECTRICAL

At +25°C, rated power supplies and a 1k $\Omega$  output load, unless otherwise specified.

|                                                            | SHC803/SHC804BM |                  |        | SHC803/SHC804CM |                                       |      |                         |

|------------------------------------------------------------|-----------------|------------------|--------|-----------------|---------------------------------------|------|-------------------------|

| PARAMETER                                                  | MIN             | TYP              | MAX    | MIN             | TYP                                   | MAX  | UNITS                   |

| SAMPLE/HOLD INPUTS (without Input E                        | Buffer)         | 1                |        |                 | •                                     |      | •                       |

| ANALOG                                                     | -               |                  |        |                 |                                       |      |                         |

| Voltage Range                                              | ±10.25          | ±11              |        | *               | *                                     |      | v                       |

| R <sub>IN</sub>                                            | 10.20           | 1.00             |        |                 | *                                     |      | kΩ                      |

| DIGITAL (HOLD, HOLD)                                       |                 |                  |        |                 |                                       |      |                         |

| V <sub>IH</sub>                                            | +2.0            |                  |        | *               |                                       |      | V                       |

| VIL                                                        | -               |                  | +0.8   |                 |                                       | *    | V                       |

| $I_{\rm IH}, V_{\rm IN} = +2.7 V$                          |                 |                  | +60    |                 |                                       | *    | μÂ                      |

| $I_{\rm II}, V_{\rm IN} = +0.4 V$                          |                 |                  | -1.2   |                 |                                       | *    | mA                      |

| SAMPLE/HOLD TRANSFER CHARACTE                              | RISTICS (with   | out Input Buffer | )      |                 | 1                                     |      |                         |

| ACCURACY                                                   |                 |                  | ,      |                 |                                       |      |                         |

| Sample Mode                                                |                 |                  |        |                 |                                       |      |                         |

| Gain                                                       |                 | _1               |        |                 | *                                     |      | V/V                     |

| Gain Error                                                 |                 |                  | ±0.1   |                 |                                       | *    | %                       |

| Temperature Coefficient                                    |                 | ±3               | ±10    |                 | ±1                                    | ±5   | ppm/°C                  |

| Linearity Error                                            |                 | ±0.001           | ±0.005 |                 | *                                     | *    | % of FSR <sup>(1)</sup> |

| Zero Offset                                                |                 | ±1               | ±5     |                 | ±0.5                                  | ±3   | mV                      |

| Temperature Coefficient                                    |                 | ±1               | ±2.5   |                 | ±0.5                                  | ±1.5 | ppm of FSR/°            |

| Hold Mode                                                  |                 |                  |        |                 |                                       |      | '                       |

| Charge Offset                                              |                 | ±2               | ±10    |                 | ±1                                    | ±5   | mV                      |

| Temperature Coefficient                                    |                 | ±3               | ±10    |                 | ±2                                    | ±4   | ppm of FSR/°            |

| Droop Rate: at +25°C                                       |                 | ±0.5             | ±5     |                 | *                                     | *    | μV/μs                   |

| +85°C                                                      |                 |                  | ±0.5   |                 |                                       | ±0.1 | mV/μs                   |

| Throughput Nonlinearity                                    |                 |                  | ±0.01  |                 |                                       | *    | % of FSR                |

| Power Supply Sensitivity <sup>(2)</sup> : ±V <sub>CC</sub> |                 |                  | ±0.002 |                 |                                       | *    | % of FSR/%V             |

| V <sub>DD</sub>                                            |                 |                  | ±0.003 |                 |                                       | *    | % of FSR/%V             |

| DYNAMIC CHARACTERISTICS                                    |                 |                  |        |                 |                                       |      |                         |

| Acquisition Time (with 10V Step)                           |                 |                  |        |                 |                                       |      |                         |

| to within: ±0.1% (±10mV)                                   |                 | 220              |        |                 | *                                     |      | ns                      |

| ±0.01% (±1mV)                                              |                 | 250              | 350    |                 | *                                     | *    | ns                      |

| Sample-to-Hold Settling Time                               |                 |                  |        |                 |                                       |      |                         |

| to within ±0.01% (±1mV)                                    |                 | 100              | 150    |                 | *                                     | *    | ns                      |

| Sample-to-Hold Transient Amplitude                         |                 | 60               | 150    |                 | *                                     | *    | mV <sub>PEAK</sub>      |

| Aperture Delay TIme <sup>(3)</sup>                         |                 | 15               | 25     |                 | *                                     | *    | ns                      |

| Aperture Uncertainty                                       |                 | ±10              | ±25    |                 | *                                     | *    | ps                      |

| Sample Mode: Output Slew Rate                              |                 | 160              |        |                 | *                                     |      | V/μs                    |

| Full Power Bandwidth                                       |                 | 1                |        |                 | *                                     |      | MHz                     |

| Small Signal Bandwidth                                     |                 | 16               |        |                 | *                                     |      | MHz                     |

| Hold Mode Feedthrough Rejection                            |                 |                  |        |                 |                                       |      |                         |

| (10V Square Wave Input)                                    | ±0.03           | ±0.005           |        |                 | *                                     |      | %                       |

| SAMPLE/HOLD OUTPUT                                         |                 |                  |        |                 |                                       |      |                         |

| Voltage Range                                              | ±10.25          | ±11              |        | *               | *                                     |      | V                       |

| Output Current                                             | ±50             |                  |        | *               |                                       |      | mA                      |

| Short Circuit Protection                                   | Ir              | definite to Comn |        |                 | *                                     |      |                         |

| Output Impedance (at DC)                                   |                 | 0.01             | 0.1    |                 | *                                     | *    | Ω                       |

| INPUT BUFFER CHARACTERISTICS (SH                           | IC803 only)     |                  | 1      |                 | 1                                     | 1    | _                       |

|                                                            |                 |                  | . –    |                 |                                       |      |                         |

| Offset Voltage                                             |                 | ±1/2             | ±5     |                 | *                                     | *    | mV                      |

| vs Temperature                                             |                 | ±1.5             | ±2.5   |                 | *                                     | *    | ppm of FSR/°            |

| Bias Current                                               |                 | 100              | ±25    |                 |                                       | *    | nA                      |

| Impedance                                                  | 140.05          | 108    5         |        | *               |                                       |      | Ω    pF                 |

| V <sub>IN</sub> Range                                      | ±10.25          | ±11              |        | î               | · · · · · · · · · · · · · · · · · · · |      | V                       |

| DYNAMIC CHARACTERISTICS                                    |                 |                  |        |                 |                                       |      |                         |

| Full Power Bandwidth                                       |                 | 320              |        |                 | *                                     |      | kHz                     |

| Slew Rate <sup>(4)</sup>                                   |                 | 10               |        |                 | *                                     |      | V/µs                    |

| Settling Time <sup>(4)</sup> to ±2mV for 10V Step          |                 | 2.5              |        |                 | *                                     |      | μs                      |

| OUTPUT                                                     |                 |                  |        |                 |                                       |      |                         |

| V <sub>out</sub> Range                                     | ±10.25          |                  |        | *               |                                       |      | V                       |

| Output Current                                             | ±10.25          |                  |        | *               | 1                                     |      | mA                      |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

## SPECIFICATIONS (CONT)

### ELECTRICAL

At +25°C, rated power supplies and a  $1k\Omega$  output load, unless otherwise specified.

|                                 | SHC803/SHC804BM |       |       | SHC803/SHC804CM |     |     |       |

|---------------------------------|-----------------|-------|-------|-----------------|-----|-----|-------|

| PARAMETER                       | MIN             | TYP   | MAX   | MIN             | TYP | MAX | UNITS |

| POWER SUPPLY REQUIREMENTS       |                 |       |       |                 |     |     |       |

| Rated Voltage: ±V <sub>cc</sub> | ±13.5           | ±15   | ±16.5 | *               | *   | *   | V     |

| V <sub>DD</sub>                 | +4.75           | +5.00 | +5.25 | *               | *   | *   | V     |

| Quiescent Current (No Load)     |                 |       |       |                 |     |     |       |

| SHC804: +V <sub>cc</sub>        |                 | 30    | 35    |                 | *   | *   | mA    |

| -V <sub>cc</sub>                |                 | 15    | 20    |                 | *   | *   | mA    |

| V <sub>DD</sub>                 |                 | 5     | 10    |                 | *   | *   | mA    |

| SHC803: +V <sub>cc</sub>        |                 | 33    | 40    |                 | *   | *   | mA    |

| -V <sub>cc</sub>                |                 | 18    | 25    |                 | *   | *   | mA    |

| V <sub>DD</sub>                 |                 | 5     | 10    |                 | *   | *   | mA    |

| Power Dissipation: SHC804       |                 | 700   | 875   |                 | *   | *   | mW    |

| SHC803                          |                 | 790   | 1100  |                 | *   | *   | mW    |

| TEMPERATURE RANGE               |                 |       |       |                 |     |     |       |

| Specification                   | -25             |       | +85   | *               |     | *   | °C    |

| Storage                         | -55             |       | +125  | *               |     | *   | °C    |

\* Specification same as SHC803/SHC804BM.

NOTES: (1) FSR means Full Scale Range and is 20V for SHC803 and SHC804. (2) Sensitivity of offset plus charge offset. (3) With respect to HOLD. For HOLD add 5ns typical. (4) With buffer connected to the sample/hold amplifier.

### **ABSOLUTE MAXIMUM RATINGS**

| Input Overvoltage ±15V                                                                                                                                                                                    |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| +V <sub>cc</sub> to V <sub>cc</sub> COMMON0 to +18V                                                                                                                                                       |  |  |  |  |

| -V <sub>cc</sub> to V <sub>cc</sub> COMMON0 to -18V                                                                                                                                                       |  |  |  |  |

| Voltage on Digital Inputs (pins 11 and 12)0.5V to +7V                                                                                                                                                     |  |  |  |  |

| Power Dissipation 1500mW                                                                                                                                                                                  |  |  |  |  |

| V <sub>DD</sub> to DCOM                                                                                                                                                                                   |  |  |  |  |

| Analog Output Indefinite Short to $V_{\text{cc}}$ COM                                                                                                                                                     |  |  |  |  |

| NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliablility. |  |  |  |  |

### PACKAGE INFORMATION<sup>(1)</sup>

| MODEL            | PACKAGE      | PACKAGE DRAWING<br>NUMBER |

|------------------|--------------|---------------------------|

| SCH803/804CM, BM | 24-Pin Metal | 113                       |

| SCH803/804BM     | 24-Pin Metal | 113                       |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

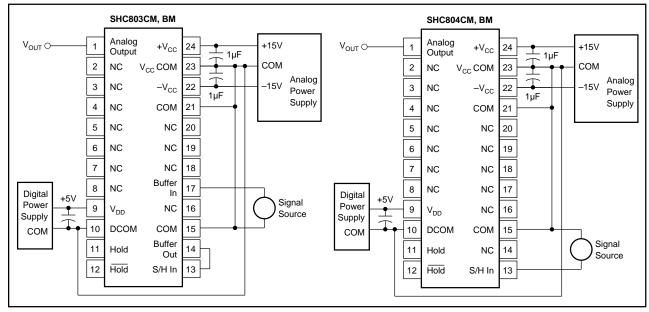

### **CONNECTION DIAGRAMS**

### **PIN ASSIGNMENTS**

| PIN | NAME                    | DESCRIPTION                                         |

|-----|-------------------------|-----------------------------------------------------|

| 1   | Sample/Hold Output      | Analog voltage output                               |

| 2   | NC                      | Not connected                                       |

| 3   | NC                      | Not connected                                       |

| 4   | NC                      | Not connected                                       |

| 5   | NC                      | Not connected                                       |

| 6   | NC                      | Not connected                                       |

| 7   | NC                      | Not connected                                       |

| 8   | NC                      | Not connected                                       |

| 9   | V <sub>DD</sub>         | Logic supply                                        |

| 10  | DCOM                    | Logic supply common                                 |

| 11  | HOLD                    | Logic "1" = HOLD                                    |

| 12  | HOLD                    | Logic "0" = HOLD                                    |

| 13  | S/H In                  | SHC804 input; for SHC803 connect<br>pin 13 to pin14 |

| 14  | Buffer Out, SHC803 only | Not connected for SHC804                            |

| 15  | СОМ                     | Signal common                                       |

| 16  | NC                      | Not connected                                       |

| 17  | Buffer In, SHC803 only  | Not connected for SHC804                            |

| 18  | NC                      | Not connected                                       |

| 19  | NC                      | Not connected                                       |

| 20  | NC                      | Not connected                                       |

| 21  | СОМ                     | Signal common                                       |

| 22  | -V <sub>cc</sub>        | -15V supply                                         |

| 23  | V <sub>cc</sub> COM     | Analog to power common, connected                   |

| 24  | +V <sub>cc</sub>        | to case<br>+15V supply                              |

## DISCUSSION OF SPECIFICATIONS

<u>Throughput Nonlinearity</u> is defined as total Hold mode, nonadjustable, input to output error caused by charge offset, gain nonlinearity, droop, feedthrough, and thermal transients. It is the inaccuracy due to these errors which cannot be corrected by Offset and Gain adjustments.

<u>Gain Error</u> is the difference between the input and output voltage magnitude (in the Sample mode) due to the amplifier gain errors.

Droop Rate is the voltage decay at the output when in the

SHC803/804BM. CM

4

Hold mode due to storage capacitor and FET switch leakage current and the input bias current of the output amplifier.

<u>Feedthrough</u> is the amount of output voltage change caused by an input voltage change when the sample/hold is in the Hold mode.

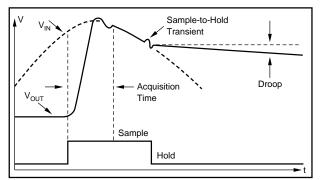

<u>Aperture Delay Time</u> is the time required to switch from Sample to Hold. The time is measured from the 50% point of the Hold mode control transition to the time at which the output stops tracking the input.

<u>Aperture Uncertainty Time</u> is the nonrepeatibility of aperture delay time.

<u>Acquisition Time</u> is the time required for the sample/hold output to settle to within a given error band of its final value when the sample/hold is switched from Hold to Sample.

<u>Charge Offset (Pedestal)</u> is the output voltage change that results from charge coupled into the Hold capacitor through the gate capacitance of the switching field effect transistor. This charge appears as an offset at the output.

<u>Sample-to-Hold Switching Transient</u> is the switching transient which appears on the output when the sample/hold is switched from Sample to Hold. Both the magnitude and the settling time of the transient are specified.

### **OPERATION**

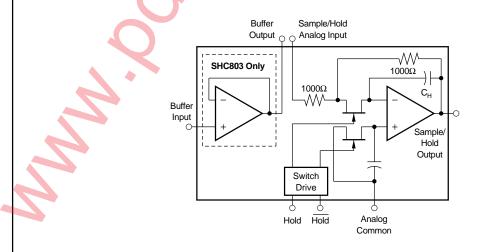

A simplified circuit diagram of SHC803/804 is shown on page 1. The SHC803 includes a noninverting unity-gain op amp to serve as a source-impedance buffer when the sample/ hold is used with CMOS analog multiplexers. The SHC804 and SHC803 are identical except for this buffer.

In the Sample (track) mode the circuit acts as a unity-gain inverting amplifier. In the Hold mode, the capacitor,  $C_{H}$ , holds the value of the output at the time the unit was switched to the Hold mode. Additional circuits compensate for switching transients and provide switch leakage current

cancellation. The amplifier provides high current drive and low output impedance to external loads.

### GAIN, OFFSET, CHARGE OFFSET

SCH803 and SCH804 have been internally-trimmed to eliminate the need for external trim potentiometers for Gain, Offset (in Sample mode) and Charge Offset (Pedestal). System Gain and Offset errors can be adjusted elsewhere in the system, at an input amplifier preceding the sample/hold, or at an analog-to-digital converter following the sample/ hold.

FIGURE 1. Definition of Acquisition Time, Droop and Sample-to-Hold Transient.

### INSTALLATION

### **GROUNDING AND BYPASSING**

SHC803 and SHC804 have four COMMON pins (pins 10, 15, 21 and 23) and all must be tied together and connected to the system analog common ( $V_{cc}$  COM) as close to the package as possible. It is preferable to have a large ground plane surrounding the sample/hold and have all four common pins soldered directly to it. Note that the metal case is internally connected to pin 23; therefore, care must be taken to avoid a ground loop if the case is allowed to contact the ground plane.

Most digital return currents pass through pin 10. Noise from the switch-drive circuit may couple directly into the main op amp summing junction, a very noise-sensitive node. Care must be taken to insure that no voltage differences occur between pin 10 and the other common pins. This is the reason pin 10 must be connected directly to the ground plane.

For the same reason, the logic supply should be kept as free of noise as possible.  $\pm V_{CC}$  supply lines (pins 24 and 22) are internally bypassed to common with 0.01µF capacitors. It is recommended that the user install additional external 0.1µF to 1µF tantalum bypass capacitors at each supply pin.

#### SAMPLE/HOLD CONTROL

A TTL logic "0" at pin 11 (or a logic "1" at pin 12) switches the SHC803/804 into the Sample (track) mode. In this mode, the device acts as a unity-gain inverting amplifier, the output following the inverse of the input. A logic "1" at pin 11 (or a logic "0" at pin 12) will switch the SHC803/804 into the Hold mode. The output voltages will be held constant at the value present when the Hold command is given.

If pin 11 is used, pin 12 must be connected to the DCOM (pin 10). If pin 12 is used, pin 11 must be tied to  $V_{DD}$ . Using the HOLD and HOLD inputs as logic function may adversely affect the charge offset (pedestal). A clean digital signal (no overshoot) at the HOLD of HOLD inputs will also reduce charge offset errors. Pins 11 and 12 present less than one standard TTL load (two LSTTL loads) to the digital drive circuit.

### **OUTPUT LOADING**

Care must be taken when loading the output of the SHC803/ 804 to avoid possible oscillations, current limiting and performance variations over temperature.

The maximum capacitive load to avoid oscillations is about 300pF. Recommended resistive load is  $500\Omega$  or more, although values as low as  $250\Omega$  may be used. Acquisition and sample-to-hold settling times are relatively unaffected by resistive loads down to  $250\Omega$  in parallel with capacitive loads up to 100pF. Higher capacitances will affect acquisition and settling times.

#### ANALOG SIGNAL SOURCE CONSIDERATIONS

The output impedance of the signal source driving the SHC804 will affect the accuracy of the sample and hold operation both statically (at DC) and dynamically. The output impedance of the signal source should be low and remain low over a wide bandwidth. A small capacitor at the driving source may help to improve the charge offset errors that are affected by dynamic source impedance.

### SHC803 BUFFER AMPLIFIER

The buffer amplifier incorporated in the SHC803 provides appropriate drive characteristics to the sample/hold amplifier. Again a 20pF to 50pF capacitor added to the output of the buffer amplifier may improve charge offset performance.

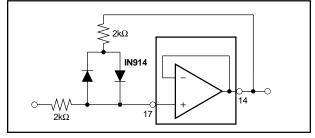

The buffer amplifier is optimized for fast settling with 10Vp-p signals. However, for step input signals greater than 10V, a protection network (Figure 2) is required to prevent the buffer from overload, resulting in excessive settling time.

The data sheet for the Burr-Brown model ADC803 analogto-digital converter contains a sample printed circuit board layout incorporating many of the above considerations.

FIGURE 2. SHC803 Buffer Amplifier Protection For Input Steps Greater Than 10V.

SHC803/804BM, CM

## APPLICATIONS

### SIGNAL DIGITIZATION

Sample/hold amplifiers are commonly used to hold input voltages to an A/D converter constant during conversion. Digitizing errors result if the analog signal being digitized varies excessively during conversion.

For example, the Burr-Brown ADC803 is a 12-bit successive-approximation converter with a  $1.5\mu s$  conversion time. To insure the accuracy of the output data, the analog input signal to the A/D converter must not change more than 1/2LSB during the conversion.

The maximum rate of change for sine wave inputs is dv/dt (max) =  $2\pi Af$  (V/s). If one allows a 1/2LSB change (2.44mV) for a ±10V input swing to the A/D converter, the allowable input rate-of-change limit would be 2.44mV/1.5 $\mu$ s = 1.63mV/ $\mu$ s. Thus the sampled sinusoidal signal frequency limit is

$f = (1.63 X 10^3)/2\pi A = 259/A(Hz)$

where A is the amplitude of the sine wave. For a  $\pm 10V$  sine wave this corresponds to a frequency of 26Hz.

A sample/hold in front of the A/D converter "freezes" the converter's input signal whenever it is necessary to make a conversion. The rate-of-change limitation calculated above no longer exists. If a sample/hold has acquired an input signal and is tracking it, the sample/hold can be commanded to hold at any instant. There is a short delay between the time the hold command is asserted and the time the circuit actually holds. This delay is called aperture delay. The hold command signal can usually be advanced in time to cause the amplifier to hold when one wants it to hold.

The uncertainty in aperture delay, called aperture jitter, is a key consideration. For the SHC803/804 there is a 25ps maximum period during which the input signal should not change, for example, more than 1/2LSB for 12-bit systems. For a  $\pm 10V$  input range (1/2LSB = 2.44mV), the input signal rate of change limitation is 2.44mV/25ps = 97.6V/µs. The equivalent input sine wave frequency is

$f = 97.6 X 10^{6}/2\pi A = 15.5/A(MHz),$

60,000 times higher than using the A/D alone.

However, there are other considerations. The resampling rate of an ADC803 is  $1.5\mu$ s (A/D conversion time) +  $0.3\mu$ s (sample/hold acquisition time) =  $1.8\mu$ s. If one samples a sine wave at the Nyquist rate this permits sampling a frequency of 278kHz. The above analysis assumed that the droop rate of the sample/hold is negligible—less than 1/2LSB during the conversion time—and that the large signal bandwidth response of the sample/hold causes negligible waveform distortion.

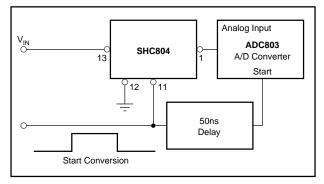

### **USING THE SHC804 WITH THE ADC803**

ADC803 is a 1.5µs, 12-bit successive approximation A/D converter. Its input circuitry has been designed to minimize high frequency current transients that appear at the input of successive approximation A/D converters. The SHC803 and SHC804 have been designed with a fast-settling, low output-

impedance amplifier to further minimize the effects of high frequency transient currents present in an output load.

A typical SHC804/ADC803 connection for high-speed digitization is illustrated in Figure 3. A short delay must occur before the A/D start command is asserted since the ADC803 makes its first conversion decision 100ns after the start command is asserted. Because the SHC804 sample-to-hold settling time is 150ns (maximum) the additional delay required is about 50ns. This can be achieved using a one-shot or by using the delay provided by the six inverters of a hex inverter integrated circuit. This combination can be triggered at rates of over 500k samples per second.

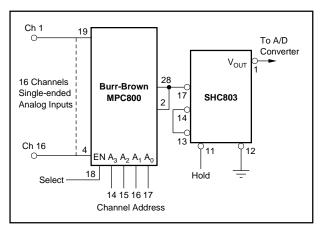

Using the input buffer of the SHC803 provides a high input impedance sample/hold for CMOS analog multiplexers such as the high speed Burr-Brown MPC800. The high input impedance of the SHC803 buffer minimizes DC errors caused by the ON resistance of the multiplexer switches and/ or relatively high impedance signal sources (Figure 4). The multiplexer can be switched to a new channel as soon as the SHC803 is switched to the Hold mode. The multiplexer/ buffer combination settles to the new input value during the sample/hold acquisition time and A/D conversion time. This "overlap" technique results in little or no loss in throughput rate.

FIGURE 3. SHC804 and ADC803 Provide Sampling Rates Over 500k Samples Per Second.

FIGURE 4. Using SHC803 With The MPC800 Analog Multiplexer.